# Submitted Jul. 25, 2011 Published Sep. 29, 2012

# COMPLEXITY CLASSIFICATIONS FOR DIFFERENT EQUIVALENCE AND AUDIT PROBLEMS FOR BOOLEAN CIRCUITS

ELMAR BÖHLER $^a,$ NADIA CREIGNOU $^b,$ MATTHIAS GALOTA $^c,$ STEFFEN REITH $^d,$ HENNING SCHNOOR $^e,$ AND HERIBERT VOLLMER $^f$

- <sup>a</sup> Theoretische Informatik, Universität Würzburg, Am Hubland, D-97030 Würzburg, Germany e-mail address: boehler@informatik.uni-wuerzburg.de

- b Aix-Marseille Université, CNRS, LIF UMR 7279, 13 288 Marseille, France e-mail address: creignou@lif.univ-mrs.fr

- <sup>c</sup> Elektrobit, Am Wolfsmantel 46, D-91058 Erlangen, Germany e-mail address: Matthias.Galota@elektrobit.com

- <sup>d</sup> Theoretische Informatik, FB DCSM, Hochschule RheinMain, Kurt-Schumacher-Ring 18, D-65197 Wiesbaden, Germany

e-mail address: Steffen.Reith@hs-rm.de

- $^e$  Institut für Informatik, Christian-Albrechts-Universität zu Kiel, Christian-Albrechts-Platz 4, 24118 Kiel

e-mail address: schnoor@ti.informatik.uni-kiel.de

f Institut f

ür Theoretische Informatik, Leibniz Universit

ät Hannover, Appelstraße 4, 30167 Hannover, Germany

e-mail address: vollmer@thi.uni-hannover.de

ABSTRACT. We study Boolean circuits as a representation of Boolean functions and consider different equivalence, audit, and enumeration problems. For a number of restricted sets of gate types (bases) we obtain efficient algorithms, while for all other gate types we show these problems are at least NP-hard.

#### 1. Introduction

The study of Boolean functions is an active research topic since more than one hundred years. Since the early papers of Shannon [RS42, Sha38] and Lupanov [Lup58] in the 1940s and 1950s, Boolean circuits (then called *switching circuits*) have been used as a computation model for Boolean functions. The computational complexity theory of Boolean circuits developed rapidly, see Savage's textbook [Sav76]. In the meantime many beautiful results have

1998 ACM Subject Classification: F.2.2.

Key words and phrases: Boolean circuits, complexity classification, isomorphism.

<sup>b</sup> Supported by the Agence Nationale de la Recherche under grant ANR-09-BLAN-0011-01.

<sup>f</sup> Supported by DFG VO 630/6-2.

been proven, e.g., in the area of lower bounds or of algebraic and logical characterizations of small circuit classes, cf. [Weg87, Vol99].

Another development of equal importance is the search for different representations (sometimes also called data structures, see, e.g., the books [MT98, Weg00]) for Boolean functions that may facilitate solving presumably hard problems. Let us explain this with an example. The well-known satisfiability problem for propositional logic is known to be NP-complete. This immediately implies that the problem, given a Boolean circuit C, to decide if there is an input for which C outputs 1 is NP-complete as well. Thus, using Boolean circuits as a representation for a Boolean function f, to determine if  $f^{-1}(1)$  is not empty appears to be a computationally hard problem. However, if we represent f by a decision tree, satisfiability can be solved in polynomial time (in the size of the decision tree). The same holds for ordered binary decision diagrams and different further types of so called branching programs, see [Weg00]. This advantage of course has its price: generally, Boolean circuits are a much more succinct way of representing Boolean functions. Nevertheless, since the pioneering work by R. E. Bryant, branching programs and in particular ordered binary decision diagrams have turned out to be a suitable representation for many application areas such as model checking, VLSI design, computer-aided design, etc; we refer the interested reader to [Weg00] for a discussion.

In this paper, a different approach is advocated. While it is known that in general satisfiability for Boolean circuits is NP-complete, there are prominent easy special cases: For example, if we consider only circuits over a monotone base, the satisfiability problem admits an efficient solution. Another example is that of linear circuits (i. e., circuits with a base of linear functions). This phenomenon was studied systematically by H. R. Lewis in 1979, who showed that satisfiability is NP-complete if the base contains or can implement the negation of implication, i. e., the function  $x \land \neg y$ . In all other cases, satisfiability has a polynomial-time algorithm. This dichotomy result holds for Boolean circuits as well as for propositional formulas. The work of Lewis has been taken up by Reith and Wagner [RW05] who examined further algorithmic problems such as the circuit value problem and the problem of counting the number of satisfying assignments.

Here we study further important algorithmic tasks for the representation of Boolean functions by Boolean circuits: First we examine the equivalence problem, i. e., the question if two given Boolean circuits represent logically equivalent Boolean functions, and the isomorphism problem, i. e., the problem if two given circuits can be made equivalent through a permutation of their input variables. While these problems are of enormous interest in the area of verification and model-checking, it should be remarked that also from a theoretical viewpoint they have a long history: they were studied by Jevons and Clifford in the 19th century and in particular the isomorphism problem became known as the "Jevons-Clifford Problem". The isomorphism problem admittedly gains its importance from a more theoretical point of view. In complexity theory, isomorphism problems in general are notorious since often they resist a precise complexity theoretic classification. Most famous of course is graph isomorphism, a candidate for an "intermediate problem" between P and the NP-complete problems. Here we obtain a dichotomy distinguishing the easy from the hard cases for isomorphism of circuits, but for the hard problems we only have a hardness result, we are not able to prove completeness for a complexity class.

A second group of problems we study concerns so called *frozen variables*. A variable x is frozen in a Boolean circuit C if C is satisfiable and all its satisfying assignments give the same Boolean value to x. We study the problem to determine if a given circuit has a variable

that is frozen. We also consider a variant that has become known recently under the name audit problem: this is the problem to decide if a given circuit has a frozen variable or is unsatisfiable. Originally the audit problem stems from the database area. One can view the value of a frozen variable as having been compromised by the results of the query expressed by the circuit. This is considered problematic with respect to data security questions (see [KPR03]). The audit problem has further practical importance also in VLSI design and testing: here, a frozen variable is a hint for a stuck-at fault and hence a manufacturing defect within the circuit.

Finally, we study a variant of the counting problem that is also relevant in practice: Instead of just determining the number of satisfying assignments we are interested in an efficient way of producing (enumerating) all such assignments. Different notions of "efficient" enumeration have been considered in a paper by Johnson et al. [JYP88]. We recall these notions here (e. g., polynomial total time, polynomial delay) and study them in the context of enumerating solutions of Boolean circuits.

For all these problems we obtain complete complexity classifications: We determine exactly those circuit bases that make the problems hard (NP-complete or even harder) and for all remaining bases we present efficient algorithms solving these problems.

The organization of the paper is as follows: In the next section we define Boolean functions and Boolean circuits. We also introduce Post's lattice of all closed classes of Boolean functions; this lattice will be our main technical tool to obtain the desired complexity results. In Sect. 3 we formally introduce all algorithmic problems that we will classify. In Sect. 4 we then turn to equivalence and isomorphism while in Sect. 5 we study all audit-like problems; Sect. 6 contains our results on enumeration. Finally, Sect. 7 contains a conclusion and presents some open problems and future research directions.

## 2. Preliminaries

2.1. Boolean functions and Post's lattice. A Boolean function is an n-ary function  $f:\{0,1\}^n \to \{0,1\}$ . In the following we will often use well-known Boolean functions as  $0, 1, \wedge, \vee, \neg, \oplus, \to$ , the implication function, and the (k+1)-ary k-threshold function  $t_k$  verifying  $t_k(x_1, \ldots, x_{k+1}) = 1$  if and only if  $\sum_{i=1}^{k+1} x_i \geq k$ .

A clone is a set of Boolean functions that is closed under superposition, i.e., it contains

A clone is a set of Boolean functions that is closed under superposition, i.e., it contains all projections (that is, the functions  $f(a_1, \ldots, a_n) = a_k$  for  $1 \le k \le n$  and  $n \in \mathbb{N}$ ) and is closed under arbitrary composition [PK79, Sze86, Pip97, Lau06]. Let B be a finite set of Boolean functions. We denote by [B] the smallest clone containing B and call B a base for [B]. The set [B] corresponds to the set of all Boolean functions that can be computed by B-circuits (as defined below). All closed classes of Boolean functions are known, as is their inclusion structure, which forms a lattice. This lattice is named after its discoverer E. Post [Pos41].

The following properties are crucial for the below definitions of the clones:

- f is c-reproducing if f(c, ..., c) = c,  $c \in \{0, 1\}$ . The functions  $\land$  and  $\lor$  are 0- and 1-reproducing, the binary exclusive or,  $\oplus$ , is 0-reproducing, but not 1-reproducing, whereas the unary negation  $(\neg)$  is neither 1- nor 0-reproducing.

- f is monotonic if  $a_1 \leq b_1, \ldots, a_n \leq b_n$  implies  $f(a_1, \ldots, a_n) \leq f(b_1, \ldots, b_n)$ . Boolean functions built up on composition of only  $\wedge, \vee, 0, 1$  are monotonic, like for instance  $g(x, y, z) \equiv x \wedge (1 \wedge (y \vee z))$ .

- f is c-separating of degree k if for all  $A \subseteq f^{-1}(c)$  of size  $|A| \le k$  there exists an  $i \in \{1,\ldots,n\}$  such that  $(a_1,\ldots,a_n) \in A$  implies  $a_i = c, c \in \{0,1\}$ . The (k+1)-ary k-threshold function  $t_k$  is 1-separating of degree k, but not 1-separating of degree k+1. For instance  $t_2(x,y,z) \equiv (x \wedge y) \vee (x \wedge z) \vee (y \wedge z)$ , which is the ternary majority function, is 1-separating of degree 2.

- f is c-separating if f is c-separating of degree  $|f^{-1}(c)|$ . The implication  $(x \to y) \equiv \neg x \lor y$  is 0-separating.

- f is self-dual if  $f(x_1, \ldots, x_n) \equiv \neg f(\neg x_1, \ldots, \neg x_n)$ . The function  $g(x, y, z) \equiv (x \land \neg y) \lor (x \land \neg z) \lor (\neg y \land \neg z)$  is self-dual.

- f is affine if  $f \equiv x_1 \oplus \cdots \oplus x_n \oplus c$  with  $c \in \{0,1\}$ . The function  $g(x,y,z) \equiv x \oplus y \oplus z \oplus 1$  is affine and self-dual.

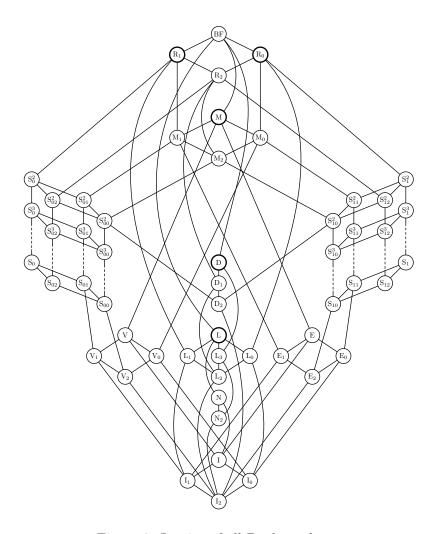

For a list of all Boolean clones see Table 1 and for their inclusion structure see Figure 2. For an extensive introduction to superposition, Post's Lattice and related problems see [BCRV03]. In the naming of the clones the semantic of single indexes is as follows. Index 2 indicates that the clone contains no constants at all. Index 0 (resp. 1) indicates that the clone contains only the constant 0 (resp. 1) but not 1 (resp. 0). Clones with no index contain both constants 0 and 1. The only exceptions to this convention are the clones D and  $D_1$  which do not contain any constants at all. The index \* stands for all valid indexes. Clones of particular importance in this paper are:

- the clone of all Boolean functions BF =  $[\land, \neg] = [\land, \lor, \neg, 0, 1]$

- the monotonic clones  $M_*$ , e.g.,  $M_2 = [\land, \lor], M = [\land, \lor, 0, 1]$

- the affine clones  $L_*$ , e.g.,  $L_2 = [x \oplus y \oplus z]$ ,  $L = [x \oplus y, 0, 1]$

- the disjunctive clones  $V_*$ , e.g.,  $V_2 = [\vee]$ ,  $V = [\vee, 0, 1]$

- the conjunctive clones  $E_*$ , e.g.,  $E_2 = [\wedge]$ ,  $E = [\wedge, 0, 1]$

- the c-reproducing clones  $R_1$  (the clone of all 1-reproducing functions),  $R_0$  (0-reproducing functions),  $R_2$  (functions that are both 1- and 0-reproducing)

- the implication clone  $S_0 = [\rightarrow]$

- the negated-implication clone  $S_1 = [x \land \neg y]$

- the self-dual clones: D self-dual,  $D_1 = D \cap R_2$ ,  $D_2 = D \cap M$

- the clones  $S_{00} = S_0 \cap R_2 \cap M = [x \vee (y \wedge z)], S_{10} = S_1 \cap R_2 \cap M = [x \wedge (y \vee z)], S_{12} = S_1 \cap R_2 = [x \wedge (y \vee \neg z)] \text{ and } S_{02} = S_0 \cap R_2 = [x \vee (y \wedge \neg z)].$

- the clones  $I_*$  containing only the identity and some constant functions, e.g.,  $I_0 = [id, 0]$

In the following we will often implicitly refer to the inclusion structure of Post's lattice. Here are some facts that we will use.

- The function  $x \oplus y \oplus z$  is a function of  $D_1$  since it is in  $L_2$  (see the base given in Table 1) and  $L_2 \subset D_1$ .

- Similarly the ternary majority function  $t_2(x, y, z) \equiv (x \wedge y) \vee (x \wedge z) \vee (y \wedge z)$  is a function of  $D_1$  since it is in  $D_2$  and  $D_2 \subset D_1$ .

- For all B such that  $S_{12} \subset [B] \subseteq R_1$  there exists a  $k \geq 2$  such that the threshold function  $t_k \in [B]$ . Indeed in this case [B] is either  $S_{12}^k$  for some  $k \geq 2$ , or  $R_1$  or  $R_2$  (which both contain  $S_{12}^2$ ).

We will often add some constant c = 0 or 1 to a clone C and consider the clone  $C' = [C \cup \{c\}]$  generated out of C and c. With Post's lattice one can determine this C' quite easily: It is

the lowest clone above C that contains c, i.e., the lowest clone above both C and  $I_c$ . As a consequence a base of C' is obtained by a base of C to which we add the constant c. The following list contains identities we will frequently use.

- BF =  $[S_1 \cup \{1\}]$ , thus  $\{x \land \neg y, 1\}$  is a base of BF.

- $S_1 = [S_{12} \cup \{0\}], \text{ thus } \{x \land (y \lor \neg z), 0\} \text{ is a base of } S_1.$

- $R_1 = [S_{12} \cup \{1\}]$ , thus  $\{x \land (y \lor \neg z), 1\}$  is a base of  $R_1$ .

- $R_0 = [S_{02} \cup \{0\}]$ , thus  $\{x \vee (y \wedge \neg z), 0\}$  is a base of  $R_0$ .

- 2.2. **Boolean circuits.** Let us now define the central objects that we deal with in this paper, namely *Boolean circuits* (see also [Vol99]):

**Definition 2.1.** Let B be a finite set of Boolean functions. A *Boolean circuit* over B, or a B-circuit is a tuple

$$C = (V, E, \alpha, \beta, o),$$

where (V, E) is a finite, acyclic, directed graph,  $\alpha \colon E \to \mathbb{N}$  is an injective function,  $\beta \colon V \to B \cup \{x_i \mid i \in \mathbb{N}\}$ , and  $o \in V$ , such that the following conditions hold:

- If  $v \in V$  has in-degree 0, then  $\beta(v) \in \{x_i \mid i \in \mathbb{N}\}$ , or  $\beta(v)$  is a 0-ary function from B,

- if  $v \in V$  has in-degree k > 0, then  $\beta(v)$  is a k-ary function in B.

Nodes in V are also called *gates*. A gate v with  $\beta(v) \in \{x_i \mid i \in \mathbb{N}\}$  is called an *input-gate*, and o is called *output-gate*. Later the function  $\alpha$  will be used to specify the order of the predecessors of a gate.

With Var(C) we denote the variables appearing in the circuit C, i.e., the set  $\{\beta(v) \mid v \in V\} \cap \{x_i \mid i \in \mathbb{N}\}.$

This definition of a Boolean circuit corresponds to the intuitive idea that a circuit consists of a set of gates which are either input gates, or compute some Boolean function (in our case, functions from B) with arguments taken from the predecessor gates. The set B is also called a base. The distinguished gate o is the output-gate, i.e., the value computed by the circuit is the result computed in this gate. The size of a circuit is the number of non-input gates. The function computed by a circuit is defined in the canonical way: Once we know the values for the input-gates, we can inductively (since the graph is acyclic) compute the value for each gate  $g \in V$ . For non-commutative functions in B, the ordering  $\alpha$  on the edges in the graph gives a well-defined function value. The following definition captures this formally:

**Definition 2.2.** Let  $C = (V, E, \alpha, \beta, o)$  be a Boolean circuit with  $Var(C) = \{x_1, \ldots, x_n\}$ , and let  $a_1, \ldots, a_n \in \{0, 1\}$ . Let v be a gate in C. We define the function  $f_v$  computed by the gate v on input  $(a_1, \ldots, a_n)$  as follows:

- If v is an input-gate, i.e.,  $\beta(v) = x_i$  for  $i \in \{1, ..., n\}$ , we define  $f_v(a_1, ..., a_n) = a_i$ .

- If v has in-degree k, and  $v_1, \ldots, v_k$  are the predecessor gates of v in C such that  $\alpha((v_1, v)) < \cdots < \alpha((v_k, v))$ , then

$$f_v(a_1,\ldots,a_n) = \beta(v)(f_{v_1}(a_1,\ldots,a_n),\ldots,f_{v_k}(a_1,\ldots,a_n)).$$

We define the function  $f_C: \{0,1\}^n \to \{0,1\}$ , the function computed by C, as  $f_o$ .

| Class                                | Definition                                                                    | Base(s)                                                                                            |

|--------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| BF                                   | all Boolean functions                                                         | $\{\wedge,\neg\}$                                                                                  |

| $R_0$                                | $\{ f \in BF \mid f \text{ is } 0\text{-reproducing} \}$                      | $\{\land,\oplus\}$                                                                                 |

| $\overline{R_1}$                     | $\{f \in BF \mid f \text{ is 1-reproducing}\}$                                | $\{\lor, x \oplus y \oplus 1\}$                                                                    |

| $\overline{R_2}$                     | $R_1 \cap R_0$                                                                | $\{\lor, x \land (y \oplus z \oplus 1)\}$                                                          |

| M                                    | $\{f \in BF \mid f \text{ is monotonic}\}\$                                   | $\{\land,\lor,0,1\}$                                                                               |

| $\overline{\mathrm{M}_{1}}$          | $M \cap R_1$                                                                  | $\{\land,\lor,1\}$                                                                                 |

| $\overline{\mathrm{M}_{\mathrm{0}}}$ | $M \cap R_0$                                                                  | $\{\land,\lor,0\}$                                                                                 |

| $M_2$                                | $M \cap R_2$                                                                  | $\{\land,\lor\}$                                                                                   |

| $S_0^n$                              | $\{ f \in BF \mid f \text{ is } 0\text{-separating of degree } n \}$          | $\{\rightarrow, \operatorname{dual}(t_n)\}$                                                        |

| $S_0$                                | $\{f \in BF \mid f \text{ is 0-separating}\}\$                                | $\{\rightarrow\}$                                                                                  |

| $S_1^n$                              | $\{ f \in BF \mid f \text{ is 1-separating of degree } n \}$                  | $\{x \wedge \overline{y}, t_n\}$                                                                   |

| $S_1$                                | $\{f \in BF \mid f \text{ is 1-separating}\}\$                                | $\{x \wedge \overline{y}\}$                                                                        |

| $S_{02}^n$                           | $S_0^n \cap R_2$                                                              | $\{x \vee (y \wedge \overline{z}), \operatorname{dual}(t_n)\}$                                     |

| $S_{02}$                             | $S_0 \cap R_2$                                                                | $\{x \lor (y \land \overline{z})\}$                                                                |

| $S_{01}^{n}$                         | $S_0^n \cap M$                                                                | $\{\operatorname{dual}(t_n), 1\}$                                                                  |

| $S_{01}$                             | $S_0 \cap M$                                                                  | $\{x \lor (y \land z), 1\}$                                                                        |

| $S_{00}^{n}$                         | $S_0^n \cap R_2 \cap M$                                                       | $\{x \lor (y \land z), \operatorname{dual}(t_n)\}$                                                 |

| $S_{00}$                             | $S_0 \cap R_2 \cap M$                                                         | $\{x \lor (y \land z)\}$                                                                           |

| $S_{12}^n$                           | $S_1^n \cap R_2$                                                              | $\{x \wedge (y \vee \overline{z}), t_n\}$                                                          |

| $S_{12}$                             | $S_1 \cap R_2$                                                                | $\{x \land (y \lor \overline{z})\}$                                                                |

| $S_{11}^{n}$                         | $S_1^n \cap M$                                                                | $\{t_n, 0\}$                                                                                       |

| $S_{11}$                             | $S_1 \cap M$                                                                  | $\{x \land (y \lor z), 0\}$                                                                        |

| $S_{10}^n$                           | $S_1^n \cap R_2 \cap M$                                                       | $\{x \land (y \lor z), t_n\}$                                                                      |

| $S_{10}$                             | $S_1 \cap R_2 \cap M$                                                         | $\{x \land (y \lor z)\}$                                                                           |

| D                                    | $\{f \mid f \text{ is self-dual}\}$                                           | $\{(x \wedge \overline{y}) \vee (x \wedge \overline{z}) \vee (\overline{y} \wedge \overline{z})\}$ |

| $D_1$                                | $D \cap R_2$                                                                  | $\{(x \wedge y) \vee (x \wedge \overline{z}) \vee (y \wedge \overline{z})\}$                       |

| $D_2$                                | $D \cap M$                                                                    | $\frac{\{(x \land y) \lor (y \land z) \lor (x \land z)\}}{\{(x \land y) \lor (x \land z)\}}$       |

| L                                    | $\{f \mid f \text{ is linear}\}$                                              | $\{\oplus,1\}$                                                                                     |

| $L_0$                                | $L \cap R_0$                                                                  | <u>{⊕}</u>                                                                                         |

| $\frac{L_1}{T}$                      | $L \cap R_1$                                                                  | <u>{</u> ↔}                                                                                        |

| $\frac{L_2}{T}$                      | $L \cap R_2$ $L \cap D$                                                       | $\frac{\{x \oplus y \oplus z\}}{\{x \oplus y \oplus z \oplus z \oplus 1\}}$                        |

| $\frac{L_3}{V}$                      | $\{f \mid f \text{ is an } \lor \text{-function or a constant function}\}$    |                                                                                                    |

|                                      | $\{f \mid f \text{ is an } \forall \text{-function of a constant function}\}$ |                                                                                                    |

| $\frac{V_0}{V_1}$                    | 10 )1 10 )1                                                                   | $\frac{\{\lor,0\}}{\{\lor,1\}}$                                                                    |

| $\frac{V_1}{V_2}$                    | $ [\{\vee\}] \cup [\{1\}] $ $ [\{\vee\}] $                                    | {V,1}<br>{V}                                                                                       |

| $\frac{\mathbf{v}_2}{\mathbf{E}}$    | $\{f \mid f \text{ is an } \land \text{-function or a constant function}\}$   | $\{\land,0,1\}$                                                                                    |

| $\frac{\mathrm{E}}{\mathrm{E}_0}$    | $\{f \mid f \text{ is an } \land \text{-tunction of a constant function}\}$   | $\{\land,0\}$                                                                                      |

| $\frac{E_0}{E_1}$                    | [{\\}] \cup [{\lambda}]                                                       | $\{\land, 1\}$                                                                                     |

| $\frac{\mathrm{E}_1}{\mathrm{E}_2}$  | [{\\}] \[ [\frac{1}{4}] \]                                                    | <u> </u>                                                                                           |

| $\frac{\mathrm{L}_2}{\mathrm{N}}$    | $[\{\neg\}] \cup [\{0\}] \cup [\{1\}]$                                        | $\{\neg,1\},\{\neg,0\}$                                                                            |

| $\frac{N_2}{N_2}$                    | [{¬}]                                                                         | <u>{</u> ¬}                                                                                        |

| $\frac{1}{I}$                        | $[\{id\}] \cup [\{1\}] \cup [\{0\}]$                                          | $\{id, 0, 1\}$                                                                                     |

| $\overline{I_0}$                     | $ [\{id\}] \cup [\{0\}] $ $ [\{id\}] \cup [\{0\}] $                           | $\frac{\{id,0,1\}}{\{id,0\}}$                                                                      |

| $\frac{I_0}{I_1}$                    | $ [\{id\}] \cup [\{1\}] $                                                     | $\frac{(id, 0)}{\{id, 1\}}$                                                                        |

| $\overline{I_2}$                     | $ [\{id\}] $                                                                  | { <i>id</i> }                                                                                      |

| -4                                   | IC)1                                                                          | ( )                                                                                                |

Figure 1: The list of all Boolean clones with definitions and bases, where  $t_n := \bigvee_{i=1}^{n+1} \bigwedge_{j=1, j\neq i}^{n+1} x_j$  and  $\operatorname{dual}(f)(a_1, \dots, a_n) = \neg f(\neg a_1 \dots, \neg a_n)$ .

Figure 2: Lattice of all Boolean clones

If the function  $f_C$  associated with a circuit C does not depend on its ith argument, we say that  $x_i$  is a *fictive* or *irrelevant* variable for the circuit.

By writing  $C(x_1, \ldots, x_n)$ , we mean that C is a circuit such that  $Var(C) \subseteq \{x_1, \ldots, x_n\}$ . For constant values  $a_1, \ldots, a_n \in \{0, 1\}$ , we also denote  $f_C(a_1, \ldots, a_n)$  by  $C(a_1, \ldots, a_n)$ . An assignment for the variables in  $C(x_1, \ldots, x_n)$  is a function  $I : \{x_1, \ldots, x_n\} \to \{0, 1\}$ . Such an assignment is also called compatible with C. We will write  $I \models C$  if  $C(I(x_1), \ldots, I(x_n)) = 1$ . In this case we also say that I is a satisfying assignment or a solution for C. We denote by Sat(C) the set of assignments satisfying C and by #Sat(C) the cardinality of this set. A circuit is satisfiable if it has a satisfying assignment. When the order of variables is clear from the context, we write an assignment simply as the tuple of binary values, i.e., with  $(a_1, \ldots, a_n)$  we denote the corresponding assignment I where  $I(x_i) = a_i$  for all relevant i. For convenience we also often write  $C(a_1, \ldots, a_n)$  when we mean  $C(a_1, \ldots, a_n)$ . Hence  $C(1^n)$  denotes the value  $C(1, \ldots, 1)$ . We sometimes view the circuit as a function of its assignments, and write C(I) = 1 if  $I \models C$ , and C(I) = 0 otherwise. In the following, let  $n \in \mathbb{N}$ , let f be an n-ary Boolean function,  $a \in \{0, 1\}$ , and  $I_1, I_2$  be

functions  $I_1, I_2: \{x_1, \ldots, x_n\} \to \{0, 1\}$ . We define  $\#_a(I) = \#\{i: 1 \le i \le n \text{ and } I(x_i) = a\}$ . For assignments  $I_1$  and  $I_2$ , we write  $I_1 \le I_2$  if  $I_1(x_i) \le I_2(x_i)$  for  $1 \le i \le n$ . Finally let  $\operatorname{dual}(I)$  be the assignment  $\operatorname{dual}(I)(x_i) = 1 - I(x_i)$ .

For a circuit C and a variable  $x \in Var(C)$ , the variable x is said to be *frozen* in C if C is satisfiable and there is a constant  $c \in \{0,1\}$  such that for all assignments I,  $I \models C$  implies I(x) = c. Similarly we define that  $V \subseteq Var(C)$  is *frozen* in C if every variable in V is frozen in C.

#### 3. Problems for propositional circuits and complexity classes

We now define the list of computational problems involving Boolean circuits that we study in this paper. All our problems are connected to the satisfiability problem and the circuit value problem defined as follows—in the following, let B be a base, i.e., a finite set of Boolean functions.

Problem: SAT<sub>C</sub>B

Instance: A B-circuit  $C(x_1, \ldots, x_n)$

Question: Is C satisfiable?

Problem:  $VAL_C(B)$

Instance: A B-circuit  $C(x_1, \ldots, x_n)$  and an assignment  $(a_1, \ldots, a_n)$

Question: Is  $f_C(a_1, \ldots, a_n) = 1$ ?

The complexity of these problems is well known:

**Proposition 3.1.** ([Lew79]) Let B be a finite set of Boolean functions. Then  $SAT_C(B)$  is NP-complete if  $S_1 \subseteq [B]$ , and solvable in P otherwise.

**Proposition 3.2** ([Lad75],[RW05]). Let B be a finite set of Boolean functions, then  $VAL_C(B) \in P$ .

We will be interested in equivalence and isomorphism problems. Let us define precisely these two notions.

**Definition 3.3.** Let  $\pi: \{x_1, \ldots, x_n\} \to \{x_1, \ldots, x_n\}$  be a permutation and  $I: \{x_1, \ldots, x_n\} \to \{0, 1\}$  be a truth assignment. We define the permuted assignment  $\pi(I)$  by  $\pi(I)(x_i) = I(\pi(x_i))$  for  $i = 1, \ldots, n$ .

**Definition 3.4.** Let  $C_1(x_1,\ldots,x_n)$  and  $C_2(x_1,\ldots,x_n)$  be *B*-circuits.

The two circuits are equivalent, denoted by  $C_1 \equiv C_2$ , if for all truth assignments  $I: \{x_1, \ldots, x_n\} \to \{0, 1\}, I \models C_1$  if and only if  $I \models C_2$ .

The two circuits are isomorphic, denoted by  $C_1 \cong C_2$  if there exists a permutation  $\pi \colon \{x_1, \dots, x_n\} \to \{x_1, \dots, x_n\}$  such that for all truth assignments  $I \colon \{x_1, \dots, x_n\} \to \{0, 1\}, I \models C_1$  if and only if  $\pi(I) \models C_2$ .

Using these equivalence relations, we define the *Boolean equivalence* and *Boolean iso-morphism* problem for *B*-circuits:

Problem:  $EQ_C(B)$

Instance: Two B-circuits  $C_1$  and  $C_2$

Question: Is  $C_1 \equiv C_2$ ?

The equivalence problem for propositional circuits or formulas is one of the standard coNP-complete problems. The complexity of the next problem we consider, the isomorphism problem, is not completely determined. It is clearly coNP-hard and lies in the second level of the polynomial hierarchy, more precisely in  $\Sigma_2^p$ . However, it is not known to be solvable in coNP, and is not complete for  $\Sigma_2^p$ , unless the polynomial hierarchy collapses [AT00]. We study the version of this problem where the inputs are restricted to B-circuits:

Problem:  $ISO_{\mathbb{C}}(B)$

Instance: Two B-circuits  $C_1$  and  $C_2$

Question: Is  $C_1 \cong C_2$ ?

The next two problems are concerned with frozen variables. As defined earlier a variable x is frozen in a satisfiable circuit if all solutions of the circuit assign x the same Boolean value. The problem of recognizing frozen variables in Boolean formulas was first studied by Jon Kleinberg, Christos Papadimitriou, and Prabhakar Raghavan in [KPR03]; their motivation to consider this problem was to ensure that database queries do not reveal information that should be kept secret. Again, we consider the version of two problems in this context where we restrict the propositional gates allowed to appear in the input circuits:

Problem:  $FV_C(B)$

Instance: A B-circuit C over a set of variables V and  $V' \subseteq V$  such that  $|V'| \ge 1$

Question: Is V' frozen in C?

If we restrict the problem  $FV_C(B)$  to instances with V' = V, then we obtain the generalized Unique Satisfiability problem over circuits. This is a natural complete problem for the class US (see [BG82]). We define the problem Unique  $SAT_C(B)$  to be the restriction of this problem to B-circuits as input.

Problem: Unique  $SAT_C(B)$ Instance: A B-circuit, C

Question: Does C have exactly one satisfying assignment?

The question of the existence of such a frozen variable is the following problem

Problem:  $\exists FV_C(B)$ Instance: A B-circuit C

Question: Is there a frozen variable in C?

Note that in the above problem  $\exists FV_C(B)$  it is necessary that the circuit is satisfiable. If we drop the restriction of being satisfiable, we have the definition of the so called *Audit problem*: Does C have a frozen variable or is C unsatisfiable?

Besides these decision problems we are also interested in the enumeration problem which asks, for a given Boolean circuit to generate the set of its satisfying assignments with no repetition.

Problem: Enum  $SAT_C(B)$ Input: A B-circuit, C

Output: All satisfying assignments of C

In the following in establishing the complexity of the decision problems defined above we need notions of the following complexity classes: Let P (NP resp.) be the class of languages which are decidable (acceptable, resp.) by deterministic (nondeterministic, resp.) Turing machines in polynomial time. For an arbitrary complexity class  $\mathcal{K}$ , let  $co\mathcal{K} = \{\overline{A} : A \in \mathcal{K}\}$ .

Recall that  $D^P = \{ L \cap L' : L \in NP, L' \in coNP \}$ , which is the second level of the Boolean hierarchy and contains both NP and coNP (see [CGH<sup>+</sup>88, CGH<sup>+</sup>89]).

For our hardness results we mostly employ  $logspace\ many-one\ reductions$ , defined as follows: A language A is logspace many-one reducible to some language B (written  $A \leq_m^{\log} B$ ) if there exists a logspace-computable function f such that  $x \in A$  if and only if  $f(x) \in B$ . We write  $A \equiv_m^{\log} B$  if  $A \leq_m^{\log} B$  and  $B \leq_m^{\log} A$ . Polynomial-time many-one reductions (written as  $A \leq_m^p B$  and  $A \equiv_m^p B$ ) are defined in the same way, except that the function f is only required to be computable in polynomial time.

For the enumeration problem polynomial time is not a suitable notion of efficiency, since the number of solutions may be exponential in the length of the circuit. For the notion of an "efficient" enumeration algorithm, we use the definitions from [JPY88]. An algorithm for the enumeration problem has polynomial total time, if the running time of the algorithm is polynomial in the length of the input circuit and in the number of its satisfying solutions. This notion is also referred to as output polynomial. An important feature of an enumeration algorithm is the ability to start generating solutions as soon as possible, and more generally to generate solutions in a regular way with a limited delay between two successive outputs. It has polynomial delay if the time needed by the algorithm between its start and the printing of the first solution, the time between the printing of each two consecutive solutions, and the time between printing the last solution and the termination of the algorithm is bounded by a polynomial in the length of the input circuit. In [JPY88] the authors exhibited polynomial-delay algorithms that used exponential space and therefore distinguished polynomial-delay algorithms using only polynomial space. In our paper polynomial-delay enumeration algorithms all work with polynomial space, hence we do not mention it explicitly. An enumeration algorithm with polynomial delay can be further required to output the elements in some order (e.g. lexicographic order) (see [JPY88]).

Let us now make explicit the main tool that we will use in order to get complexity classifications.

**Proposition 3.5.** Let **Prob** be one of the decision problems introduced above, and let  $B_1, B_2$  be finite sets of Boolean functions such that  $B_1 \subseteq [B_2]$ . Then  $\mathbf{Prob}(B_1) \leq_m^{\log} \mathbf{Prob}(B_2)$ . In particular, if  $[B_1] = [B_2]$ , then  $\mathbf{Prob}(B_1) \equiv_m^{\log} \mathbf{Prob}(B_2)$ .

Proof. Since all of the problems that we study in this paper only consider the function computed by the corresponding input circuits, it is clear that a transformation converting a circuit into an equivalent one leaves the properties considered in these decision problems invariant. Observe that if  $B_1$  and  $B_2$  are finite sets of Boolean functions such that  $B_1 \subseteq [B_2]$ , then every function from  $B_1$  can be expressed as a  $B_2$ -circuit, its so-called  $B_2$ -representation. Thus we can, in logarithmic space, convert any  $B_1$ -circuit into an equivalent  $B_2$ -circuit in replacing every gate of the original circuit (which is a function from  $B_1$ ) by its  $B_2$ -representation. This concludes the proof. Note that since  $B_1$  and  $B_2$  are not part of the input the cost of computing the  $B_2$ -representations of the functions of  $B_1$  is a not taken into account.

Since the above result shows that the complexity of the problems we study does not depend on the particular base of a clone that we consider, we sometimes write  $\mathbf{Prob}(C)$  for a clone C. For example, we write  $\mathrm{SAT}_{\mathbf{C}}(\mathrm{BF})$  to denote the satisfiability for a set B with

[B] = BF, e.g., for  $SAT_C(\{\land, \lor, \neg\})$ . Due to the above, choosing a different base B of BF results in a problem with the same complexity.

As a consequence in order to get a complete classification for  $\mathbf{Prob}(B)$  for every finite set B it is enough to examine all possible clones. When we show a hardness result for  $\mathbf{Prob}(C)$  for some clone C, then hardness also holds for every finite set B such that  $C \subseteq [B]$ . Also when we show tractability of  $\mathbf{Prob}(C)$ , then tractability also holds for every finite set B such that  $B \subseteq [C]$ .

We also note that a similar result as Proposition 3.5 applies to the enumeration problem. For example, if  $B_1 \subseteq [B_2]$ , and there is a polynomial-delay enumeration algorithm for  $B_2$ -circuits, then there also is a polynomial-delay enumeration algorithm for  $B_1$ -circuits.

#### 4. Equivalence- and isomorphism problems

In this section we use the inclusion structure of all closed classes (see Figure 2) to determine the complexity of  $EQ_{\mathbb{C}}(B)$  step by step. Similarly we are able to give lower bounds for the isomorphism problem of B-circuits.

The following lemma will be a useful fact in our proofs—the lemma follows from the simple observation that for the equivalence- or isomorphism problems, consistently swapping 0s and 1s does not change the complexity. Let us first introduce some notation. If f is an n-ary Boolean function, then  $\operatorname{dual}(f)$  denotes the Boolean function such that  $\operatorname{dual}(f)(x_1,\ldots,x_n) = \neg f(\neg x_1,\ldots,\neg x_n)$ . For a set B of Boolean functions, let  $\operatorname{dual}(B) = \{\operatorname{dual}(f) \mid f \in B\}$ .

**Lemma 4.1.** Let B be a finite set of Boolean functions. Then  $EQ_C(B) \equiv_m^{\log} EQ_C(dual(B))$  and  $ISO_C(B) \equiv_m^{\log} ISO_C(dual(B))$ .

Let us first identify the tractable cases. The next proposition says that when besides constants only  $\vee$ -functions or only  $\wedge$ -functions or only  $\oplus$ -functions are allowed, equivalence and isomorphism are easily checkable.

**Proposition 4.2.** Let B be a finite set of Boolean functions. If  $B \subseteq E$  or  $B \subseteq V$  or  $B \subseteq L$  then  $EQ_C(B)$  and  $ISO_C(B)$  are tractable.

*Proof.* If B only contains to  $\vee$ -functions ( $\wedge$ -functions,  $\oplus$ -functions resp.), the basic idea is that we can first compute an explicit normal form for the functions computed by such a B-circuit. This normal form then easily allows to determine equivalence or isomorphism.

First let  $B \subseteq V$ . Let  $C_1(x_1, \ldots, x_n)$  and  $C_2(x_1, \ldots, x_n)$  be two B-circuits. The Boolean functions described by  $C_1$  and  $C_2$  can be expressed as follows:  $f_{C_1}(x_1, \ldots, x_n) = a_0 \vee (a_1 \wedge x_1) \vee \cdots \vee (a_n \wedge x_n)$  and  $f_{C_2}(x_1, \ldots, x_n) = b_0 \vee (b_1 \wedge x_1) \vee \cdots \vee (b_n \wedge x_n)$ , where  $a_1, \ldots, a_n, b_1, \ldots, b_n \in \{0, 1\}$ .

The values of  $a_i$  and  $b_i$ , where  $0 \le i \le n$ , can be determined easily by using the following simple facts:  $a_0 = 0$  ( $b_0 = 0$ , resp.) iff  $f_{C_1}(0^n) = 0$  ( $f_{C_2}(0^n) = 0$ , resp.) and  $a_i = 0$  ( $b_i = 0$ , resp.) for  $1 \le i \le n$  iff  $a_0 = 0$  ( $b_0 = 0$ , resp.) and  $f_{C_1}(0^{i-1}10^{n-i}) = 0$  ( $f_{C_2}(0^{i-1}10^{n-i}) = 0$ , resp.). This can be checked in polynomial time with the help of VAL<sub>C</sub>(B) as an oracle. Since VAL<sub>C</sub>(B) is tractable (see Proposition 3.2) we conclude that the normal forms can be computed efficiently. Now, clearly  $(C_1, C_2) \in \text{EQ}_{\mathbb{C}}(B)$  iff either  $a_0 = b_0 = 1$  or  $a_0 = b_0 = 0$  and  $a_i = b_i$  for  $1 \le i \le n$ , and similarly,  $(C_1, C_2) \in \text{ISO}_{\mathbb{C}}(B)$  iff either  $a_0 = b_0 = 1$  or  $|\{i \mid a_i = 1, 1 \le i \le n\}| = |\{i \mid b_i = 1, 1 \le i \le n\}|$  and  $a_0 = b_0 = 0$ . Thus we conclude that  $\text{EQ}_{\mathbb{C}}(B)$  and  $\text{ISO}_{\mathbb{C}}(B)$  are tractable.

Tractability for  $B \subseteq E$  now follows immediately from the above using Lemma 4.1.

Finally let  $B \subseteq L$  and let  $C_1$  and  $C_2$  be B-circuits. The Boolean functions described by the B-circuits  $C_1(x_1,\ldots,x_n)$  and  $C_2(x_1,\ldots,x_n)$  can be expressed as follows:  $f_{C_1}(x_1,\ldots,x_n) = a_0 \oplus (a_1 \wedge x_1) \oplus \cdots \oplus (a_n \wedge x_n)$  and  $f_{C_2}(x_1,\ldots,x_n) = b_0 \oplus (b_1 \wedge x_1) \oplus \cdots \oplus (b_n \wedge x_n)$ , where  $a_1,\ldots,a_n,b_1,\ldots,b_n \in \{0,1\}$ . Similar to the above cases the values  $a_i$  and  $b_i$  for  $0 \le i \le n$  can be determined by a  $\oplus L$ -calculation, since we know that  $VAL_C(B)$  is tractable. In particular  $a_0 = f_{C_1}(0,\ldots,0), \ b_0 = f_{C_2}(0,\ldots,0), \ a_i = f_{C_1}(0^{i-1}10^{n-i}) \oplus a_0$  and  $b_i = f_{C_2}(0^{i-1}10^{n-i}) \oplus b_0$ , where  $1 \le i \le n$ . Now, clearly  $(C_1,C_2) \in EQ_C(B)$  iff  $a_i = b_i$  for  $0 \le i \le n$ , and  $(C_1,C_2) \in ISO_C(B)$  iff  $a_0 = b_0$  and  $|\{i \mid a_i = 1, 1 \le i \le n\}| = |\{i \mid b_i = 1, 1 \le i \le n\}|$ . Again, both problems are tractable.

The main step in obtaining hardness for the remaining cases now is to show that both equivalence and isomorphism are hard for monotone functions. This is the statement of the next lemma.

**Lemma 4.3.**  $EQ_{C}(\{\vee, \wedge\})$  and  $ISO_{C}(\{\vee, \wedge\})$  are  $\leq_{m}^{\log}$ -hard for coNP.

*Proof.* We prove that 3-TAUT, the problem of deciding whether a 3-DNF formula is a tautology, is logspace reducible to  $EQ_C(\{\lor,\land\})$  and  $ISO_C(\{\lor,\land\})$ . Since 3-TAUT is well known to be coNP-hard this will complete the proof.

Let  $H(x_1, ..., x_n)$  be a 3-DNF formula with  $Var(H) = \{x_1, ..., x_n\}$ . Let  $C(x_1, ..., x_n, y_1, ..., y_n)$  be the circuit obtained from H in replacing every occurrence of a negated variable  $\neg x_i$  by the fresh variable  $y_i$ . Note that C is a  $\{\lor, \land\}$ -circuit that can have fictive variables. Define  $C_1(x_1, ..., x_n, y_1, ..., y_n) = \bigwedge_{i=1}^n (x_i \lor y_i)$  and  $C_2(x_1, ..., x_n, y_1, ..., y_n) = C_1 \land C$ . Observe that  $Sat(C_2) \subseteq Sat(C_1)$ .

We claim that H is a tautology if and only if  $C_1 \equiv C_2$  if and only if  $C_1 \cong C_2$ . Suppose first that H is a tautology. We prove that every assignment that sets at least one of  $x_i$  and  $y_i$  to true for every  $i=1,\ldots,n$  satisfies C, thus proving  $C_1 \equiv C_2$  and a fortiori  $C_1 \cong C_2$ . Let I be such an assignment. Consider the assignment  $\tilde{I}$  defined by  $\tilde{I}(x_i) = I(x_i)$  and  $\tilde{I}(y_i) = 1 - I(x_i)$  for  $i = 1,\ldots,n$ . Observe that  $\tilde{I}$  satisfies C since H is a tautology. Moreover since for every i,  $I(x_i) + I(y_i) \geq 1$  we have  $I \geq \tilde{I}$ . Therefore by monotonicity I satisfies C as well.

Conversely, suppose that H is not a tautology. We prove that  $\#\mathrm{Sat}(C_1) \neq \#\mathrm{Sat}(C_2)$ , thus proving  $C_1 \ncong C_2$  and a fortiori  $C_1 \not\equiv C_2$ . Let I be an assignment that does not satisfy H. Consider I' defined by  $I'(x_i) = I(x_i)$  and  $I'(y_i) = 1 - I(x_i)$  for  $i = 1, \ldots, n$ . Observe that I' satisfies  $C_1$  but not  $C_2$ . Since  $\mathrm{Sat}(C_2) \subseteq \mathrm{Sat}(C_1)$ , this proves that  $\#\mathrm{Sat}(C_2) < \#\mathrm{Sat}(C_1)$ .

The next three propositions generalize the hardness result from Lemma 4.3.

**Proposition 4.4.** Let B be a set of Boolean functions such that  $S_{10} \subseteq [B]$  or  $S_{00} \subseteq [B]$ , then  $EQ_C(B)$  and  $ISO_C(B)$  are  $\leq_m^{\log}$ -hard for coNP.

Proof. First let  $S_{10} \subseteq [B]$ . By Figure 1 we know that  $g(x,y,z) = x \land (y \lor z)$  is a base of  $S_{10}$ . Since  $g(x,y,y) = x \land y$  and  $g(1,x,y) = x \lor y$  we know that  $\land \in [B]$  and  $\lor \in [B \cup \{1\}]$ . Therefore according to Proposition 3.5 and Lemma 4.3 we get that  $EQ_C(B \cup \{1\})$  and  $ISO_C(B \cup \{1\})$  are coNP-hard. We now reduce these problems respectively to  $EQ_C(B)$  and  $ISO_C(B)$ . Let  $C_1(x_1,\ldots,x_n,1)$  and  $C_2(x_1,\ldots,x_n,1)$  be two  $B \cup \{1\}$ -circuits. Let v be a fresh variable that will be used to replace the constant 1. Let  $C'_1(x_1,\ldots,x_n,v) = C_1(x_1,\ldots,x_n,v) \land v$  and  $C'_2(x_1,\ldots,x_n,v) = C_2(x_1,\ldots,x_n,v) \land v$ . Since  $\land \in [B]$ ,  $C'_1$  and  $C'_2$  can be represented as B-circuits, and their B-representation can be computed in logarithmic

space, see proof of Proposition 3.5. It is obvious that  $C_1 \equiv C_2$  if and only if  $C_1' \equiv C_2'$ . If  $C_1 \cong C_2$  then clearly  $C_1' \cong C_2'$ . Conversely if  $C_1' \cong C_2'$  then there is a permutation  $\pi \colon \{x_1, \ldots x_n, v\} \to \{x_1, \ldots x_n, v\}$  such that for all assignment I,  $I \models C_1'$  if and only if  $\pi(I) \models C_2'$ . Since the value of v is fixed to 1 in every satisfying assignment one can suppose w.l.o.g. that  $\pi(v) = v$ . In this case we clearly have that for all assignment I,  $I \models C_1$  if and only if  $\pi(I) \models C_2$ , thus showing that  $C_1 \cong C_2$ .

Now let  $S_{00} \subseteq [B]$ . By inspecting Figure 2 we obtain that  $S_{10} \subseteq [B]$  as well, or  $S_{10} \subseteq \text{dual}([B])$ . According to Lemma 4.1 the proof is then completed.

**Proposition 4.5.** Let B be a finite set of Boolean functions such that  $D_2 \subseteq [B] \subseteq D$ , then  $EQ_C(B)$  is  $\leq_m^{\log}$ -hard for coNP.

Proof. Due to Lemma 4.3, we know that  $\mathrm{EQ_C}(\{\wedge,\vee\})$  is  $\leq_m^{\log}$ -hard for coNP. Hence let  $C_1$  and  $C_2$  be  $\{\wedge,\vee\}$ -circuits, where  $\mathrm{Var}(C_1)\cup\mathrm{Var}(C_2)=\{x_1,\ldots,x_n\}$ . By Figure 1 we know that  $t_2(x,y,z)=(x\wedge y)\vee(x\wedge z)\vee(y\wedge z)$ , the ternary majority function, is a base for  $\mathrm{D}_2$ . Using the equalities  $t_2(x,y,0)=x\wedge y$  and  $t_2(x,y,1)=x\vee y$ , we can transform  $C_1$  and  $C_2$  into equivalent  $\{t_2,0,1\}$ -circuits in logarithmic space. For ease of notation, we denote these (equivalent) circuits with  $C_1(x_1,\ldots,x_n,0,1)$  and  $C_2(x_1,\ldots,x_n,0,1)$  again. We note that due to the above transformation, every application of  $t_2$  in  $C_1$  or  $C_2$  has exactly one constant argument.

We now construct  $\{t_2\}$ -circuits  $C_1'$  and  $C_2'$  such that  $C_1 \equiv C_2$  if and only if  $C_1' \equiv C_2'$ . Due to Proposition 3.5, this completes the proof.

Let u and v be fresh variables that will be used to replace the constants 0 and 1 that appear in  $C_1$  and  $C_2$ . Now define

```

C_1'(x_1,\ldots,x_n,u,v) = t_2(v,C_1(x_1,\ldots,x_n,u,v),u) and C_2'(x_1,\ldots,x_n,u,v) = t_2(v,C_2(x_1,\ldots,x_n,u,v),u).

```

By construction,  $C_1'$  and  $C_2'$  are  $\{t_2\}$ -circuits. We prove that  $C_1 \equiv C_2$  if and only if  $C_1' \equiv C_2'$ .

First assume that  $C_1 \equiv C_2$ , and let I be an assignment for  $\{x_1, \ldots, x_n, u, v\}$ . If I(u) = I(v), then  $I \models C'_1$  iff  $I \models C'_2$  iff I(u) = I(v) = 1. Now consider the case that  $I(u) \neq I(v)$ . Since  $t_2$  is a self-dual function it is sufficient to consider the case I(u) = 0 and I(v) = 1. In this case  $I \models C'_i$  iff  $I \models C_i$  for i = 1, 2, and hence  $I \models C'_1$  iff  $I \models C'_2$  since  $C_1 \equiv C_2$ .

Conversely, suppose that  $C_1 \not\equiv C_2$ . Then we can suppose that there exists an assignment I that satisfies  $C_1$  but not  $C_2$ . Extend I to I' by setting I'(u) = 0 and I'(v) = 1. It is easy to see that I' satisfies  $C'_1$  but not  $C'_2$ , thus proving that  $C'_1 \not\equiv C'_2$ .

We have a similar result for the isomorphism problem.

**Proposition 4.6.** Let B be a finite set of Boolean functions such that  $D_2 \subseteq [B] \subseteq D$ , then  $ISO_C(B)$  is  $\leq_m^{\log}$ -hard for coNP.

While the proof of this proposition uses essentially the same reduction as above, it is technically more involved and requires some technical results. We will reduce from the isomorphism problem for  $\{\land, \lor\}$ -circuits, which we know to be coNP-hard due to Lemma 4.3. However, in the proof of Proposition 4.6, we will need some special properties of the instances of  $ISO_{\mathbb{C}}(\{\lor, \land\})$  that we reduce from. We therefore present a series of intermediate technical results that allow us to restrict the instances of  $ISO_{\mathbb{C}}(\{\lor, \land\})$  as required.

First we need to introduce some new notion.

**Definition 4.7.** A pair of two variables  $\{s,t\}$  is dominant for a circuit C, if every truth assignment I with  $I(s) = I(t) = \alpha$  satisfies the circuit C if and only if  $\alpha = 1$ .

The following lemma gives some easy properties of dominant pairs. The proof of the lemma is straight-forward.

#### Lemma 4.8.

- (1) Let C be a circuit, and let  $\{s,t\}$  and  $\{s',t'\}$  be two dominant pairs for C. Then  $\{s,t\} \cap \{s',t'\} \neq \emptyset$ .

- (2) Let  $C_1$  and  $C_2$  be two circuits such that  $C_1 \cong C_2$  via a permutation  $\pi$ . If  $\{s,t\}$  is a dominant pair for  $C_1$ , then  $\{\pi(s), \pi(t)\}$  is a dominant pair for  $C_2$ .

*Proof.* For the first part, assume that  $\{s,t\} \cap \{s',t'\} = \emptyset$ . Then there is an assignment I with I(s) = I(t) = 0, and I(s') = I(t') = 1. Since  $\{s,t\}$  is dominant for C, it follows that  $I \not\models C$ . On the other hand, since  $\{s',t'\}$  is dominant for C as well, we know that  $I \models C$ , a contradiction. The second part is trivial.

Next we need the following result, which says that the isomorphism problem remains hard for monotone functions even for some restricted instances.

**Lemma 4.9.** ISO<sub>C</sub>( $\{\lor, \land\}$ ) is  $\leq_m^{\log}$ -hard for coNP, even when instances are restricted to pairs of circuits  $(C_1, C_2)$  where neither  $C_1$  nor  $C_2$  implies or is implied by one variable, and further  $\#\text{Sat}(C_1) + \#\text{Sat}(C_2) < 2^n$  where n is the number of variables in  $C_1$ , which is the same as the number of variables in  $C_2$ .

*Proof.* We reduce the problem  $ISO_C(\{\vee, \wedge\})$ , which is coNP-hard due to Lemma 4.3, to the same problem with restrictions on the instances.

Let  $(C_1^0, C_2^0)$  be a pair of  $\{\vee, \wedge\}$ -circuits given as an instance of  $ISO_{\mathbb{C}}(\{\vee, \wedge\})$ .

Without loss of generality one can suppose that they have the same number of variables, n, and that  $C_i^0$  is of the form  $C_i^{0'} \wedge (y \wedge z)$ . Thus  $C_i^0$  has fewer than  $2^{n-1}$  solutions. Since both  $C_i^0$  are monotone, we can, in polynomial time, verify whether  $C_1^0$  or  $C_2^0$  are constant. If one of them is, then  $C_1^0 \cong C_2^0$  is true if and only if they are equivalent to the same constant. Hence we assume that neither  $C_1^0$  nor  $C_2^0$  is constant. For  $i \in \{1,2\}$ , we now rewrite  $C_i^0$  into

$$C_i = t_2(z_1, z_2, C_i^0),$$

where  $t_2$  is the ternary majority function.

We will show that the  $C_i$ 's have the desired properties, and that  $C_1^0 \cong C_2^0$  if and only if  $C_1 \cong C_2$ , thus concluding the proof.

Clearly, since the outmost operator of  $C_1$  and  $C_2$  is the majority function, and neither  $C_1^0$  nor  $C_2^0$  are constant, it follows that no variable implies or is implied by one of the  $C_i$ . Obviously,  $\#\mathrm{Sat}(C_i) = 2 \cdot \#\mathrm{Sat}(C_i^0) + 2^n$ , since the solutions of  $C_i$  are exactly those of  $C_i^0$  extended with  $z_1 \neq z_2$  (giving two solutions for each solution of  $C_i^0$ ), plus all  $2^n$  assignments setting  $z_1 = z_2 = 1$ . Since  $\#\mathrm{Sat}(C_i^0) < 2^{n-1}$ , it follows that  $\#\mathrm{Sat}(C_i) < 2^n + 2^n = 2^{n+1}$ . Therefore,  $\#\mathrm{Sat}(C_1) + \#\mathrm{Sat}(C_2) < 2^{n+2}$  as required (note that n+2 is the number of variables appearing in  $C_1$  and  $C_2$ ).

It remains to show that  $C_1^0 \cong C_2^0$  if and only if  $C_1 \cong C_2$ . The left-to-right direction is trivial, by extending the permutation to be the identity on  $\{z_1, z_2\}$ . For the other direction, assume that  $C_1 \cong C_2$  via a permutation  $\pi$ . Observe that  $\{z_1, z_2\}$  is a dominant pair for both circuits. If  $\pi(\{z_1, z_2\}) = \{z_1, z_2\}$ , then since  $z_1$  and  $z_2$  are symmetric, we can assume that  $\pi(z_i) = z_i$ , and  $\pi$  restricted to the original variables establishes  $C_1^0 \cong C_2^0$ .

Hence assume  $\pi(\{z_1, z_2\}) \neq \{z_1, z_2\}$ . According to Lemma 4.8,  $\pi(\{z_1, z_2\}) \cap \{z_1, z_2\} \neq \emptyset$ . Since  $z_1$  and  $z_2$  are symmetric, we assume without loss of generality that  $\pi(\{z_1, z_2\}) = \{z_1, x\}$  for a variable x of  $C_2$ .

We prove that  $C_2^0$  is equivalent to x. First let I be an assignment to the variables in  $C_2^0$  with I(x) = 1, we prove that  $I \models C_2^0$ . For this, consider the assignment  $I^+$  which extends I by  $I^+(z_1) = 1$  and  $I^+(z_2) = 0$ . Since  $\{z_1, x\}$  is dominant, it follows that  $I^+ \models C_2$ , and thus  $I \models C_2^0$ . Therefore, x implies  $C_2^0$ . For the other direction, let I be an assignment with I(x) = 0, we show that  $I \not\models C_2^0$ . We extend I to  $I^+$  by setting  $I^+(z_1) = 0$  and  $I^+(z_2) = 1$ . Since  $\{z_1, x\}$  is dominant for  $C_2$ , it follows that  $I^+ \not\models C_2$ , hence we know that  $I \not\models C_2^0$ , and thus  $C_2^0$  is equivalent to x as claimed.

Therefore,  $C_2$  has exactly three relevant variables (recall that a variable x is relevant for a circuit C, if there are assignments  $I_1$  and  $I_2$  such that  $I_1(x') = I_2(x')$  for all variables  $x' \neq x$ , and  $I_1 \models C$  and  $I_2 \not\models C$ , i.e., if the value of the function computed by the circuit in fact depends on x).

Since  $C_2 \cong C_1$ , we know that  $C_1$  also has exactly three relevant variables. Hence  $C_1^0$  has exactly one relevant variable, and since we also know that  $C_1^0$  is a monotone circuit, it follows that  $C_1^0$  is equivalent to a single variable. In particular,  $C_1^0 \cong C_2^0$  as claimed.  $\square$

We need a last technical result. This lemma allows us, in the later proof of Proposition 4.6, to use a similar argument as in the above proof of Lemma 4.9: In both proofs it is essential that we can control the possible dominant pairs of a circuit that is of the form  $t_2(x_1, x_2, C)$ , where  $t_2$  is the ternary majority function and C is some circuit. In the proof of Lemma 4.9, we knew the dominant sets of  $t_2(z_1, z_2, C_i^0)$  since  $z_1$  and  $z_2$  did not appear in  $C_i^0$ . In the proof of Proposition 4.6, the situation will be a bit more complicated, and we will need the following lemma to ensure that the dominant pairs in the circuits resulting from our reduction are exactly the ones that we need.

**Lemma 4.10.** If  $C(x_1, ..., x_n, 1, 0)$  is a circuit that does not imply a variable and is not implied by a variable, then  $\{u, v\}$  is the only dominant pair for

$$C' = t_2(u, C_2(x_1, \dots, x_n, u, v), v),$$

where u and v are new variables.

We note that a circuit C implies a variable if and only if the function computed by C is 1-separating, and is implied by a variable if and only if the function computed by C is 0-separating We note that for the ternary majority function  $t_2$ , all pairs of two distinct variables are dominant.

*Proof.* We use the following notation: For an assignment I for C, with  $I^+$  we denote the assignment I extended with  $I^+(u) = 1$  and  $I^+(v) = 0$ . By construction it follows that  $I \models C$  if and only if  $I^+ \models C'$ .

Clearly,  $\{u, v\}$  is dominant for C'. Let  $\{u', v'\} \neq \{u, v\}$  be dominant for C'. Due to Lemma 4.8, we know that  $\{u, v\} \cap \{u', v'\} \neq \emptyset$ .

First assume  $u \in \{u,v\} \cap \{u',v'\}$ , then  $\{u',v'\} = \{u,x\}$  for a variable x of C. We prove that x implies C. Hence let I(x) = 1. By construction, we have that  $I^+(u) = 1$ , and  $I^+(x) = I(x) = 1$ . Since  $\{u,x\}$  dominates C', it follows that  $I^+ \models C'$ . Due to the above, this means that  $I \models C$ . Hence x implies C, a contradiction.

Similarly, assume that  $v \in \{u, v\} \cap \{u', v'\}$ , then  $\{u', v'\} = \{v, x\}$  for a variable x of C. We claim that C implies x. Hence let I be an assignment with  $I \models C$ , and assume that I(x) = 0. From the above it follows that  $I^+ \models C'$ . On the other hand, we have that

$I^+(x) = I^+(v) = 0$ , and since  $\{v, x\}$  dominates C', this implies  $I^+ \not\models C'$ , a contradiction. Therefore, C indeed implies x, which is a contradiction to the prerequisites of the lemma.  $\square$

We are now in a position to prove Proposition 4.6.

*Proof.* As in the proof of Proposition 4.5 we get that  $ISO_C(B \cup \{0,1\})$  is coNP-hard, and we reduce this problem to  $ISO_C(B)$ . Let  $C_1(x_1, \ldots, x_n, 0, 1)$  and  $C_2(x_1, \ldots, x_n, 0, 1)$  be two  $B \cup \{0, 1\}$ -circuits. According to Lemma 4.9 one can suppose that neither  $C_1$  nor  $C_2$  implies or is implied by one variable, and further that  $\#Sat(C_1) + \#Sat(C_2) < 2^n$  where n is the number of variables in  $C_1$ , which is the same as the number of variables in  $C_2$ .

Let u and v be fresh variables, and let

$$C'_1(x_1,\ldots,x_n,u,v)=t_2(u,C_1(x_1,\ldots,x_n,u,v),v)$$

and

$$C'_2(x_1,\ldots,x_n,u,v)=t_2(u,C_2(x_1,\ldots,x_n,u,v),v).$$

As mentioned in the earlier proof of Lemma 4.9, this construction is very similar to what we used there. The major difference lies in the role of the variables that are used in the application of the newly introduced majority function: In the proof of Lemma 4.9, we used new variables  $z_1$  and  $z_2$  that did not appear anywhere else, and whose role was symmetric. In fact, the proof of Lemma 4.9 only works since  $z_1$  and  $z_2$  did not appear in the circuits  $C_i^0$  considered in that proof.

In the current proof, the situation is different: Here, the variables u and v do appear in the circuits  $C_i(x_1, \ldots, x_n, u, v)$ , and they are clearly not symmetric—they "simulate" the values 0 and 1, respectively. In the remainder of the current proof, we make crucial use of the facts established in Lemma 4.9, namely, that the circuits  $C_1$  and  $C_2$  are not implied by, or imply, a variable. This then allows us to apply Lemma 4.10 and ensure that  $\{u, v\}$  is the only dominant pair of  $C'_i$ .

Another difference is that in the current proof, the circuits  $C_i(x_1, \ldots, x_n, u, v)$  are indeed D<sub>2</sub>-circuits, where in the earlier result, the majority function was applied to (almost) arbitrary  $\{\land, \lor\}$ -circuits.

We prove  $C_1 \cong C_2$  if and only if  $C_1' \cong C_2'$ . It is obvious that if  $C_1 \cong C_2$  then  $C_1' \cong C_2'$ . Conversely, suppose that  $C_1' \cong C_2'$ . Then there exists a permutation  $\pi \colon \{x_1, \ldots, x_n, u, v\} \to \{x_1, \ldots, x_n, u, v\}$  such that for every truth assignment  $I \colon \{x_1, \ldots, x_n, u, v\} \to \{0, 1\}$  it holds that  $I \models C_1'$  if and only if  $\pi(I) \models C_2'$ . Observe that because of the majority function, the pair  $\{u, v\}$  is dominant for both circuits  $C_1'$  and  $C_2'$ . According to Lemma 4.10 we have then  $\{\pi(u), \pi(v)\} = \{u, v\}$ . Suppose that  $\pi(u) = v$  and  $\pi(v) = u$ . Let  $\#C_1'$  be the number of truth assignments satisfying  $C_1'$  that set u to 0 and v to 1, and  $\#C_2'$  be the number of truth assignments satisfying  $C_1'$  that set u to 1 and v to 0. Since  $C_1'$  and  $C_2'$  are isomorphic through a permutation  $\pi$  such that  $\pi(u) = v$  and  $\pi(v) = u$  we have  $\#C_1' = \#C_2'$ . We have  $\#C_1' = \#\{I \mid I(u) = 0, I(v) = 1 \text{ and } C_1(I(x_1), \ldots, I(x_n), 0, 1) = 1\}$  and  $\#C_2' = \#\{J \mid J(u) = 1, J(v) = 0 \text{ and } C_2(J(x_1), \ldots, J(x_n), 1, 0) = 1\}$ . Observe that  $\#C_1' = \#\text{Sat}(C_1)$ , while

$$#C_2' = \#\{I : \{x_1, \dots, x_n\} \to \{0, 1\} \mid C_2(I(x_1), \dots, I(x_n), 1, 0) = 1\}$$

=  $\#\{I : \{x_1, \dots, x_n\} \to \{0, 1\} \mid C_2(1 - I(x_1), \dots, 1 - I(x_n), 0, 1) = 0\},$

since  $C_2$  is a  $B \cup \{0,1\}$ -circuit and B contains only self-dual functions. Therefore  $\#C_2' = 2^n - \#\operatorname{Sat}(C_2)$ . But  $\#C_1' = \#C_2'$  implies  $\#\operatorname{Sat}(C_1) = 2^n - \#\operatorname{Sat}(C_2)$ , i.e.,  $\#\operatorname{Sat}(C_1) + 2^n - \#\operatorname{Sat}(C_2)$

$\#Sat(C_2) = 2^n$ , which is not the case by assumption, thus providing a contradiction. Therefore  $\pi(u) = u$  and  $\pi(v) = v$ . With this it is easy to see that  $C'_1 \cong C'_2$  implies that  $C_1 \cong C_2$ through the same permutation  $\pi$ .

By a careful inspection of Figure 2 we see that Propositions 4.2, 4.4, 4.5, and 4.6 cover all cases. This leads us to the following classification theorems for the complexity of the equivalence- and isomorphism- problems of B-circuits:

**Theorem 4.11.** Let B be a finite set of Boolean functions.

- (1) If  $B \subseteq E$  or  $B \subseteq V$  or  $B \subseteq L$  then  $EQ_C(B)$  and  $ISO_C(B)$  are tractable.

- (2) In all other cases  $EQ_C(B)$  is  $\leq_m^{\log}$ -complete for coNP and  $ISO_C(B)$  is  $\leq_m^{\log}$ -hard for coNP.

#### 5. Results for audit-like problems

This section covers our results about the problems related to the audit and frozen variable problems. We start with the following basic facts about complexity upper bounds.

**Proposition 5.1.** For every finite set B of Boolean functions, the following upper bounds hold:

- (1)  $FV_C(B) \in D^P$ , (2)  $\exists FV_C(B) \in D^P$ ,

- (3) Unique  $SAT_C(B) \in D^P$ , and (4)  $AUDIT_C(B) \in coNP$ .

As an auxiliary problem we will first examine the generalization of the satisfiability problem  $SAT_{C}^{*}(B)$ , which asks whether a B-circuit has a satisfying assignment different from the all 1's one. This problem was examined in [CH97] in the constraint setting.

**Theorem 5.2.** Let B be a finite set of Boolean functions. Then  $SAT_{\mathbb{C}}^*(B)$  is NP-complete if  $S_{12} \subseteq [B]$ , and solvable in P otherwise.

*Proof.* First assume  $S_{12} \subseteq [B]$ . In this case by looking at Post's lattice (see Figure 2) we know that  $[S_{12} \cup \{0\}] = S_1$ , hence following Proposition 3.1,  $SAT_C(S_{12} \cup \{0\})$  is NPcomplete. We will now reduce  $SAT_C(S_{12} \cup \{0\})$  to  $SAT_C(S_{12})$ . Given an  $(S_{12} \cup \{0\})$ circuit  $C(x_1,\ldots,x_n,0)$  we use a new variable x as a replacement for the constant 0. Thus we obtain an  $S_{12}$ -circuit  $C'(x_1,\ldots,x_n,x)$ . Looking at Table 1 we see that the Boolean function  $g(x,y,z) = x \wedge (y \vee \bar{z})$  belongs to  $S_{12}$ . Hence, let  $\hat{C}$  be the  $S_{12}$ -circuit defined by  $\hat{C} = g(\cdots g(g(C', x_1, x), x_2, x), \cdots, x_n, x)$ . Observe that  $\hat{C}$  is equivalent to  $C' \wedge (x_1 \vee \bar{x}) \wedge (x_1 \vee \bar{x})$  $(x_2 \vee \bar{x}) \wedge \cdots \wedge (x_n \vee \bar{x})$ . Observe now that C has a satisfying assignment if and only if there is an assignment different from the all 1's one that satisfies  $\hat{C}$ . We conclude that  $SAT_{C}^{*}(S_{12})$ is NP-hard, thus showing that  $SAT_{\mathbb{C}}^*(B)$  is NP-complete for all B such that  $S_{12} \subseteq [B]$ .

If  $B \subseteq M$ , then an n-ary circuit C has a satisfying assignment besides the all-1assignment if and only if it has a satisfying assignment of the form  $1^{i}01^{n-i-1}$ . Hence  $SAT_{C}^{*}(B)$  can be solved with n evaluations of the circuit C.

If  $B \subseteq L$ , we can use the linear normal form  $0 \oplus \bigoplus_{i=1}^n c_i x_i$ , which is obviously polynomial time computable, to solve  $SAT_{\mathbb{C}}^*(B)$  efficiently.

If  $B \subseteq D$  or  $B \subseteq S_0^2$  then we claim that each n-ary B-circuit has at least  $2^{n-1}$  satisfying assignments, which obviously makes  $SAT_C^*(B)$  tractable. If  $B \subseteq D$  the claim holds for any self-dual circuit has exactly  $2^{n-1}$  solutions. If  $B \subseteq S_0^2$ , note that for every B-circuit and compatible assignment I, if I does not satisfy C, then  $\operatorname{dual}(I)$  does. Indeed, assume that both I and  $\operatorname{dual}(I)$  do not satisfy C. Since C is a B-circuit, and  $B \subseteq S_0^2$ , we know that the function described by C is 0-separating of degree 2. Thus every set S with |S| = 2 and  $S \subseteq C^{-1}(\{0\})$  is 0-separating. The set S defined as  $S\{(I(x_1), \ldots, I(x_n)), (\operatorname{dual}(I)(x_1), \ldots, \operatorname{dual}(I)(x_n))\}$  meets these conditions, and hence is 0-separating. From the definition, it follows that there is some  $i \in \{1, \ldots, n\}$  such that  $I(x_i) = \operatorname{dual}(I)(x_i)$ , which is a contradiction to the definition of  $\operatorname{dual}(I)$ . In particular, the number of solutions of such a circuit is at least  $2^{n-1}$ .

Next we want to study problems which are related to the concept of frozen variables.

**Lemma 5.3.** Let B be a finite set of Boolean functions. If  $D_1 \subseteq [B] \subseteq D$  or  $S_{02} \subseteq [B] \subseteq R_1$ , then  $FV_C(B)$  and  $\exists FV_C(B)$  are coNP-complete.

*Proof.* Observe that for all B that satisfy the conditions above all B-circuits are trivially satisfiable, hence  $FV_C(B)$  and  $\exists FV_C(B)$  are in coNP.

Let  $S_{02} \subseteq [B] \subseteq R_1$ . We will reduce the coNP-complete problem (see Proposition 3.1)  $\overline{SAT_C(R_0)}$  to  $\exists \ FV_C(B)$  and  $FV_C(B)$ . Recall that due to the very end of Section 2.1, we know that  $\{x \lor (y \land \overline{z}), 0\}$  is a base of  $R_0$ . Hence let C be a circuit over  $\{x \lor (y \land \overline{z}), 0\}$ . We build a new circuit C' out of C by taking a fresh variable x and by replacing every occurrence of 0 in C with x. Then C' is an  $S_{02}$ -circuit. Since  $V_2 \subseteq S_{00} \subseteq S_{02}$  we have  $V \in [B]$  (see Figure 2), and hence  $C' \lor x$  can be converted into an equivalent B-circuit Note that the only possibly frozen variable in  $C' \lor x$  is x, since with setting x to true, every possible assignment to the other variables satisfies the circuit. Finally, x is a frozen variable in  $C' \lor x$  if and only if C is not satisfiable.

Now let  $D_1 \subseteq [B] \subseteq D$ . We will reduce the coNP-complete problem  $EQ_C(D_1)$  (see Theorem 4.11) to  $\exists FV_C(B)$  and  $FV_C(B)$ . For that let  $C_1$  and  $C_2$  be two n-ary  $D_1$ -circuits. Let x be a fresh variable and let  $C' = x \oplus C_1 \oplus C_2$ . Since  $x \oplus y \oplus z$  is a function in  $D_1$  (see Figure 2), C' is a  $D_1$ -circuit. Consider now the  $D_1$ -circuit  $C''(x, y, z) = t_2(x, y, z)$  (remind that  $t_2 \in D_1$ ). The reduction  $\Phi$  works as follows:

$$\Phi(C_1, C_2) = \begin{cases} C'' & \text{, if } C_1(0^n) \neq C_2(0^n) \text{ or } C_1(1^n) \neq C_2(1^n) \\ C' & \text{otherwise} \end{cases}$$

We claim that  $C_1 \equiv C_2$  holds if and only if  $\Phi(C_1, C_2) \in \exists \operatorname{FV}_C(D_1)$  if and only if  $(\Phi(C_1, C_2), \{x\}) \in \operatorname{FV}_C(B)$ . For that let  $C_1 \equiv C_2$ , then  $\Phi(C_1, C_2) = C'$ . Since  $C_1 \oplus C_2 \equiv 0$  the formula C' is satisfied if and only if x is satisfied. Thus x is a frozen variable and therefore  $\Phi(C_1, C_2) \in \exists \operatorname{FV}_C(B)$  and  $(\Phi(C_1, C_2), \{x\}) \in \operatorname{FV}_C(B)$ . On the other hand, if  $C_1 \not\equiv C_2$  then we have two cases. If  $C_1(0^n) \not= C_2(0^n)$  or  $C_1(1^n) \not= C_2(1^n)$  then  $\Phi(C_1, C_2) = C''$ , which is a circuit without frozen variables. If  $C_1(0^n) = C_2(0^n)$  and  $C_1(1^n) = C_2(1^n)$  then  $\Phi(C_1, C_2) = C'$ . Since  $C_1 \not\equiv C_2$ , there is an assignment  $\alpha \in \{0, 1\}^n$  such that  $C_1(\alpha) \not= C_2(\alpha)$ . Therefore  $1 = 0 \oplus C_1(\alpha) \oplus C_2(\alpha) = 1 \oplus C_1(0^n) \oplus C_2(0^n) = 1 \oplus C_1(1^n) \oplus C_2(1^n)$  and there is no frozen variable in C'.

The following is our main classification result for the problem that asks if there is any frozen variable:

**Theorem 5.4.** Let B be a finite set of Boolean functions.

- (1) If  $B \subseteq L$ ,  $B \subseteq M$ , or  $B = S_{12}$  then  $\exists FV_C(B)$  is tractable.

- (2) If  $[B] = S_1$ , then  $\exists FV_C(B)$  is NP-complete.

- (3) If  $S_1 \subset [B]$  then  $\exists FV_C(B)$  is  $D^P$ -complete.

- (4) In all other cases  $\exists FV_C(B)$  is coNP-complete.

### Proof.

(1) If  $B \subseteq L$  then in a B-circuit there is a frozen variable if and only if exactly one of the variables of its linear normal form has a coefficient of 1. Note that the linear normal form can easily be computed from the circuit using simulation (see proof of Proposition 4.2).

Now let  $B \subseteq M$  and let  $C(x_1, \ldots, x_n)$  be a B-circuit. By monotonicity the variable  $x_i$  is frozen if and only if  $C(1^n) = 1$  and  $C(1^{i-1}01^{n-i}) = 0$ . Moreover the satisfiability of a monotonic C can be easily tested. If  $B = S_{12} = R_1 \cap S_1$  then every B-circuit C is satisfiable and has a frozen variable because C is 1-separating.

- (2) Note that an  $S_1$ -circuit has a frozen variable by definition if and only if it is satisfiable and it is therefore equivalent to  $SAT_C(B)$ , which is known to be NP-complete by Proposition 3.1.

- (3) Let B such that  $S_1 \subset [B]$ . It is obvious, that  $\exists FV_C(B)$  is in  $D^P$ . Let us now introduce the problem SATP(B):

$$SATP(B) = \{ (C_1, C_2) : C_1 \text{ and } C_2 \text{ are } B\text{-circuits}$$

and  $(C_1 \in SAT_C(B) \text{ xor } C_2 \in SAT_C(B)) \}$

By definition SATP(B) is in D<sup>P</sup> and is D<sup>P</sup>-complete as far as SAT<sub>C</sub>(B) is NP-complete (cf. [CGH<sup>+</sup>88, CGH<sup>+</sup>89]). We now reduce SATP(B) to  $\exists$  FV<sub>C</sub>(B), thus completing the proof. Since S<sub>1</sub>  $\subset$  [B], there is a  $k \geq 2$  such that  $t_k$  is in [B]. Let  $C_1$  and  $C_2$  be B-circuits which are m- and n-ary respectively. Now define  $C = t_k(C_1, C_2, x_1, \ldots, x_{k-1})$ , where  $x_i$  is a fresh variable for  $1 \leq i \leq k-1$ . Clearly C is a B-circuit. Next we show that this transformation gives the needed reduction.

If  $C_1, C_2$  are both satisfiable then there are assignments  $\alpha \in \{0, 1\}^m$  and  $\beta \in \{0, 1\}^n$  such that  $C_1(\alpha) = C_2(\beta) = 1$ . Then none of the variables of  $C_1$  is frozen in C, since  $C(\gamma \beta 1^{k-1}) = 1$  for all  $\gamma \in \{0, 1\}^m$ . The same argumentation holds for all variables in  $C_2$ . Furthermore for all  $1 \le i \le k-1$  it holds that  $x_i$  is not frozen in C, since  $C(\alpha \beta 1^{i-1} 01^{k-i-1}) = C(\alpha \beta 1^{k-1}) = 1$ .

If  $C_1, C_2$  are both unsatisfiable, then C is not satisfiable and therefore has no frozen variables.

Suppose now without loss of generality  $C_1$  is satisfiable and that  $C_2$  is not, then  $C \equiv C_1 \wedge x_1 \wedge \cdots \wedge x_{k-1}$  and obviously at least all of the  $x_i$ 's  $(1 \le i \le k-1)$  are frozen.

(4) If  $D_1 \subseteq [B] \subseteq D$  or  $S_{02} \subseteq [B] \subseteq R_1$ , then  $\exists FV_C(B)$  is coNP-complete because of Lemma 5.3. The only remaining case is  $S_{12} \subset [B] \subseteq R_2$ . Then B-circuits are trivially satisfiable and therefore  $\exists FV_C(B) \in \text{coNP}$ . The proof of the lower bound is similar to Case 3, but this time the reduction starts with  $\overline{SAT_C^*(B)}$ , which is coNP-complete (see Theorem 5.2). Since  $S_{12} \subset [B] \subseteq R_1$  there is a  $k \geq 2$  such that  $t_k$  is in [B]. Let  $C(x_1,\ldots,x_n)$  be a B-circuit with the variables  $x_1,\ldots,x_n$ . Let  $C'=t_k(C,y_1,\ldots,y_k)$ ,  $C''=\left(\left(\bigwedge_{i=1}^k y_i\right) \vee \neg\left(\bigwedge_{j=1}^n x_j\right)\right)$  and  $G(x_1,\ldots,x_n,y_1,\ldots,y_k)=C'\wedge C''$ . Observe that C'' and therefore G can be converted into equivalent B-circuits, because  $A \in [B]$  and  $A \cap \{x_1,\ldots,x_n\} \in A$ .

If C is unsatisfiable, then because of C' then G is satisfiable only by setting  $y_i$  to 1 for all  $1 \le i \le k$ . The same holds if C has the all-1 assignment as only satisfying assignment because of C''. Hence in both cases all  $y_i$  are frozen.

On the other hand, if there is an  $\alpha \in \{0,1\}^n$  such that  $\alpha \neq (1,\ldots,1)$  and  $C(\alpha)=1$  then none of the  $x_i$ 's is frozen  $(1 \leq i \leq n)$ , since G can be satisfied by just setting all the  $y_i$ 's to 1. Furthermore, for each  $j \in \{1,\ldots,k\}$  holds  $G(\alpha 1^{j-1}01^{k-j})=1=G(\alpha 1^k)$ , hence none of the  $y_j$ 's is frozen.

Concerning the variant of the above problem, where the frozen variable is part of the input, we obtain the following classification:

**Theorem 5.5.** Let B be a finite set of Boolean functions.

- (1) If  $B \subseteq M$  or  $B \subseteq L$ , then  $FV_C(B)$  is tractable,

- (2) else if  $S_1 \subseteq [B]$ , then  $FV_C(B)$  is  $D^P$ -complete,

- (3) else  $FV_C(B)$  is coNP-complete.

*Proof.* If  $B \subseteq M$  or  $B \subseteq L$ , then the argumentations from Theorem 5.4.1 hold.

We have seen in Lemma 5.3 that if  $D_1 \subseteq [B] \subseteq D$  or  $S_{02} \subseteq [B] \subseteq R_1$ , then  $FV_C(B)$  is coNP-complete.

This leaves the coNP-hardness of  $FV_C(B)$  for B such that  $S_{12} \subseteq [B]$  and the  $D^P$ -hardness of  $FV_C(B)$  for all B such that  $S_1 \subseteq [B]$  to show. We reduce  $FV_C(R_1)$  to  $FV_C(S_{12})$  ( $FV_C(BF)$  to  $FV_C(S_1)$ , resp.). For that, let C be a circuit over the  $R_1$ -base  $\{x \land (y \lor \overline{z}), 1\}$  (over the BF-base  $\{x \land \overline{y}, 1\}$ , resp.) and let V be the set of variables used in C. Build a circuit C' by taking a variable x that is not contained in C and replace every occurrence of 1 in C by x. Then  $C' \land x$  is an  $S_{12}$ -circuit (an  $S_1$ -circuit, resp.), which can only be satisfied by assignments that set x to 1. For all these assignments,  $C' \land x$  is satisfied if and only if C is satisfied. Therefore  $(C, V) \in FV_C(R_1)$  ( $(C, V) \in FV_C(BF)$ , resp.) if and only if  $(C' \land x, V) \in FV_C(S_{12})$  ( $(C' \land x, V) \in FV_C(S_1)$ , resp.).

To obtain a classification for the audit problem, we first note the following link between the complexity of the problem  $\exists FV_C(B)$  and the audit problem:

**Proposition 5.6.** Let B be an arbitrary set of Boolean functions, then